# 低温ポリシリコン薄膜形成技術の 開発

The Development of Low temperature Formation of Polycrystalline Silicon Thin Films

桐村 哉\* 浩 久保田 小野田 敏\* H. Kirimura K. Kubota M. Onoda 小 寺 志\* 鞍谷 橋 高 英 治 T. Kotera N. Kuratani E. Takahashi 均\* 中 米 田 渡邊 也 ⊞ T. Watanabe Y. Tanaka H. Yoneda 潔\* 岸 田 茂 明 緒 方 S. Kishida K. Ogata

#### Synopsis

We have developed a new technology for a low-temperature growth of poly crystalline silicon (p-Si) thin films used for a thin film transistor (TFT) which can expect the application to a high performance display, such as a high quality large-sized display, a sheet computer, etc. This new deposition technique is the method that can crystallize a silicon film at lower temperature than that of the conventional method. This p-Si film is performed by the deposition of silicon atoms generated by the high density and low potential silane (SiH4) gas with the ion beam irradiation. We introduce about the development situation of the deposition of p-Si films and the product specification for 600x720mm substrates.

#### 1.まえがき

フラットパネルディスプレイは、省エネルギー・省スペース・軽量の観点から液晶ディスプレイ(LCD)が大きな進展を遂げ、2001年度には2.3兆円市場にまで成長した。さらに本格的なマルチメディア時代を迎えて、オフィスユースに加えて一般家庭へのインターネットの普及から、フラットパネルディスプレイの需要増加が確実となり、2010年には7.8兆円市場になると予想されている(こ)。LCDの他、最近では大型TVとしてプラズマディスプレイ(PDP)やまだ小型の開発段階ではあるが有機EL、FED等、次世代のディスプレイの開発が国内外で活発に行われている。

液晶ディスプレイの消費電力は従来のCRT(ブラウン管)やPDPの半分で、膨大なディスプレイ市場を考えると、その省エネルギー効果は莫大な数値となり、社会的

にもその普及、発展が期待される。しかし21インチ以上の大型ディスプレイにおいて現在のLCDでは、各画素にアモルファスシリコン薄膜トランジスタ(a-Si-TFT)を用いていることからスイッチング速度が遅い為、高精細・動画対応が困難であったり、TFTサイズを小さくできない為、高輝度化・省エネ(光源)化が困難である。CRTの表示性能と同様のLCDの普及を促進するには大画面・高輝度・高精細・動画対応を克服すべきこれら開発課題が残っている。

この問題を解決でき、さらにはシートコンピューターやシステム液晶と呼ばれる次世代の多機能化した液晶ディスプレイへの応用が期待できる技術として、低温ポリシリコン薄膜が注目されている。ポリシリコンは、従来のアモルファスシリコンと異なり、~数100nmの結晶粒が緻密に結合する多結晶構造から成る。例えばトランジ

<sup>\*</sup>技術開発研究所 プロセス研究センター

スタ特性では応答速度(電子移動度)がアモルファスシリコンの数100倍の性能を有し、単結晶シリコンに匹敵する薄膜と言える。

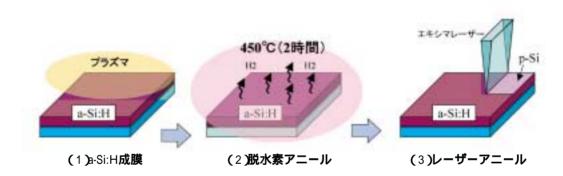

ポリシリコン薄膜は従来から、高価な石英基板上に高温下(1000 )で成長させる固相成長法や、600 程度の熱CVD法により形成することができる。しかし、フラットパネルディスプレイのような応用では、安価なガラス基板(歪点:600 )を使用するため、従来の固相成長法や熱CVD法を用いることができない。近年、ガラス基板上に低温(500 以下)でもポリシリコン膜が形成できるレーザーアニール(ELA)法が開発された。レーザーアニール法は、短波長(紫外光)レーザー光を利用して、瞬時にシリコン薄膜を融解させ、結晶成長させる手法である。図1にこの手法の詳細を示す。(1)まず低温(200 )下でプラズマCVD法を用いて、ガラス基板上にアモルファスシリコン薄膜を形成する。(2)形成されたアモルファスシリコン薄膜には10%以上の水素を含んで

いる為、約450 で2時間程度の脱水素熱処理を行い、水 素濃度を1%程度にまで減少させる。(3)レーザーアニー ルは主に高出力のエキシマレーザー装置を用いて、複雑 な光学系でライン状に加工されたレーザービームをガラ ス基板上に走査しながら照射して、アモルファスシリコ ンを結晶化したポリシリコン膜に改質する。しかしこの 手法の欠点は、各種の高価な装置が複数台必要で、また 高額のメンテナンスが必要になる点、大きなガラス基板 全面に均一にレーザーを照射することが困難であるため 均一な電気特性を持つポリシリコン膜が形成できない点 が上げられる。これはディスプレイにとって致命的な色 むらの問題点として現れる。よってレーザーアニール法 は、生産性が低く、将来必要となる大面積(1m級)のガ ラス基板に均一にポリシリコン膜を形成することは極め て困難となる。そこで当社では、これら問題点を解決で きる、ポリシリコン直接成膜法を開発した。以下にその 技術を紹介する。

図1 現状のシリコン膜の結晶化に用いられているレーザーアニール法

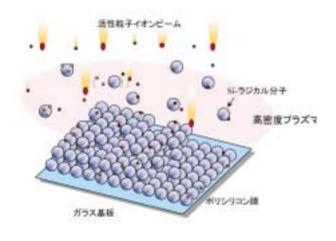

図2 成膜原理

## イオンアシストプラズマCVD法による低温 ポリシリコン薄膜形成

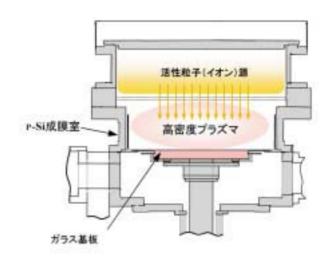

当社が開発したポリシリコン直接成膜法の原理を図2に示す。従来のレーザーアニール法では、短波長の紫外光のエネルギーによってアモルファスシリコン膜を溶解させるのに対し、当社の技術では、シリコン原子の堆積と同時に、活性粒子ピームによる核形成効果を利用している。シリコン原子はガラス基板上でイオンピームからの励起エネルギーを受けて安定な結晶構造サイトに移動することで結晶成長する。ここで与えるイオンのエネルギーは数keV以下の比較的低いエネルギーで、構造欠陥を発生しにくい。よってこの手法では、本来高温(1000 程度)での励起プロセスを低温プロセス(400以下)に置き換えることができる。この原理を実現する

装置の概略図を図3に示す。シリコン膜を堆積する為に は、自社独自の構造を持つ電極に高周波を導入して、原 料のシランガス(SiH4)を高密度プラズマにより高効率で 分解する。分解されたシリコン原子は、アモルファス表 面を持つガラス基板上には結晶成長しにくい。そこでプ ラズマ上部に設置された活性粒子イオン源から照射する 励起用イオンビームのエネルギーを受けて、ガラス基板 の最表面に核成長が起こり、ガラス基板表面から結晶成 長が起こる。イオンビームは高周波励起方式やフィラメ ント励起方式により高密度のプラズマから引き出され、 基板に照射する。ここでガス圧は通常のプラズマCVD より約二桁低い1Pa以下であり、イオンビームの到達 率は約50%以上と見積もられる。又、シリコン原子を分 解する高密度プラズマ密度は、通常のプラズマCVDの 一桁高い密度~10<sup>10</sup>cm³でプラズマポテンシャルは40eV 以下のプラズマ特性が得られている。このようにシリコ ン原子を生成するプラズマは高密度でしかも低ポテンシ ャルであることから、結晶成長に有利な低ダメージで高 い分解効率を持つプラズマを実現している。

#### 3.開発の状況

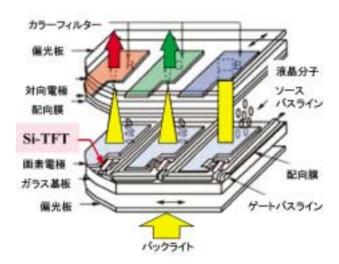

アクティプマトリックス液晶ディスプレイは、各画素 に薄膜トランジスタが組み込まれている。フルカラー、 階調表示を精度良く行うには、このRGB三原色の各トラ ンジスタのスイッチングにより制御される。例えば、 SXGA表示のLCDでは、2,949,120(1,280×RGB×768)個の Si-TFTが画面全面に作り込まれている(図4)。現在の HDテレビのように動画表示をこの解像度で表示するに は、このTFTのスイッチング速度を現在のアモルファス シリコンの約10倍に高める必要がある。TFTのスイッチ ングを表現する値として電子移動度がある。例えば現在 のアモルファスシリコンTFTの場合、移動度は0.5cm²/V·s 程度である。一方レーザーアニール法により形成された ポリシリコンTFTは100cm²/V·sである。最近では単結晶 並の移動度500cm²/V・sを実現するポリシリコンの報告が なされている。このように高速のTFTが実現できると、 画素信号を制御する駆動回路までがディスプレイ一体に 形成することが可能となる。これが最近、小型で高解像 度の表示性能が可能なポリシリコンTFT液晶ディスプレ イ(デジタルカメラ、ノートPC、携帯電話に採用)である。

## 3・1 大型基板対応ポリシリコン成膜装置の開発

現在当社では、液晶ディスプレイ業界でいう第3世代基板サイズ600×720mm対応の試作機を製作し開発中である。ガラス基板は全て自動化されたロボットで成膜プロセス室まで搬送され、成膜処理後、大気カセットまで回収する枚様式マルチチャンバー成膜システムを開発している。(図5)

図3 低温ポリシリコン成膜装置

図4 液晶ディスプレイ構造

図5 枚様式マルチチャンパー成膜システム

液晶用TFT生産ラインに対応するためには、装置の全自動化が必須である。成膜する上で必要なプロセスパラメーターとして、プロセスガス流量、プロセス圧力、プラズマ発生用高周波電力、基板温度などがあるが、高品質なp-Si薄膜を再現性良く成膜するためには、これらプロセスパラメーターを正確に制御する必要がある。

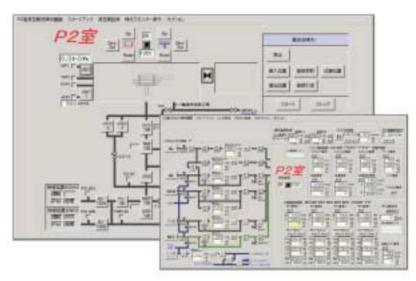

自動運転操作はマンマシンインターフェイスとなるホストコンピューターより行い、上記プロセスパラメーターの入力レシピ画面(図6)より一括入力し、レシピ通りの成膜を自動で行う。成膜プロセス室へのガラス基板の搬出入についても自動搬送を行うと同時に

基板管理が可能である。また、装置のインターロック 監視機能、装置運転状態の自動データ記録機能などを 含め、装置運転の一括管理することが可能であり、生 産装置化に向けた制御システムの開発を進めている。

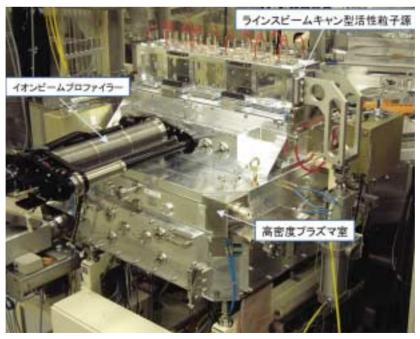

成膜プロセス室の外観を図7の写真で紹介する。製品ではフッ素系のガスを用いたドライクリーニング方式を採用している。よってチャンバーは全てアルミ、ニッケル系の耐食性材料を使用している。また新規開発の大型基板対応のイオン源を搭載している。このイオン源は、従来の面照射方式でなく、ラインビームを偏向電極により走査して、基板全面に均一にイオンビームを照射できる方式を採用した。

図6 制御システム画面一例

図7 成膜プロセス室外観写真

#### 3・2 ポリシリコン薄膜の直接成膜技術の開発

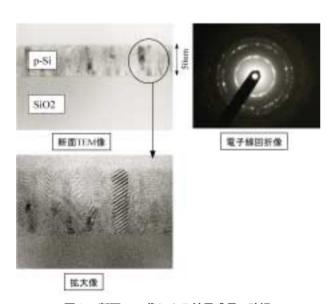

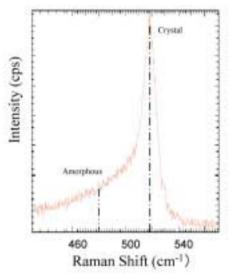

本手法で成膜したポリシリコン膜の現状の特性を紹介する。図8にガラス基板上に成膜した50nmの厚みの断面TEM像を示す。成膜原理で紹介したように、ガラス基板上の極表層から、シリコン結晶粒の成長が明確に確認できる。結晶のグレンサイズは横方向で20nm、縦方向では膜厚サイズ(50nm)のグレンサイズに成長していることが確認できる。又、中央の電子線回折でも多結晶を示す回折パターンが確認できる。特に基板との界面付近にアモルファス相がなく、緻密な結晶粒が成長していることが明確となった。シリコンの結晶評価に有効なラマン分光分析のスペクトルを図9に示す。スペクトルは明らかに結晶シリコンを示す520cm・のシャープなピークを示し、460~500cm・のスペクトルの

肩は微結晶、アモルファス相の混在を示している。

ラマンスペクトルに見られる結晶性は、ポリシリコン薄膜の成膜条件によって変化することが判っている。結晶性がイオンビームの照射条件や成膜時のプラズマ状態によって制御できる。

尚、TFT特性を示す簡易的な代替値のホール移動度特性で移動度評価を行った結果、最も高い結晶性を示す膜で、ホール移動度30cm²/V·sの値が得られている。ホール移動度の値は、ラマンスペクトルでの結晶性の向上が移動度の向上に一致していることを確認している。

大面積対応の製品で最も重要視されるのが均一性である。以下に、基板サイズ600×720mm面内でのポリシリコン膜の膜厚均一性、膜質(結晶性)均一性について説明する(2)。

図8 断面TEM像による結晶成長の確認

図9 ラマン分光分析による結晶性評価結果

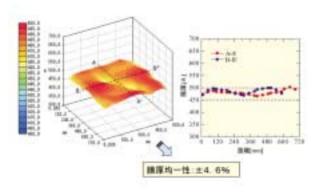

図10 膜厚均一性評価

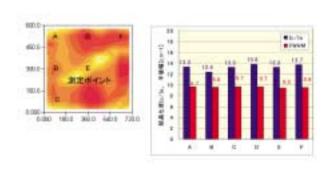

図11 膜質(結晶性)均一性評価

#### 膜厚均一性

図10に標準的な成膜条件での膜厚均一性の評価結果を示す。液晶ディスプレイメーカーではTFT工程(エッチング等)での製造精度を考慮して、薄膜の膜厚均一性は±5%を要求される。今回、開発した装置では面内膜厚均一性は、±4.6%の特性が得られている。材料ガスの導入構造、高周波電極の形状・配置の最適化が最も重要なファクターとなる。

## 膜質(結晶性)均一性

同様に基板サイズ600×720mm面内でのポリシリコン膜の結晶性をラマン分光分析法により評価した結果を図11に示す。結晶性評価は、基板の各ポイントでのラマンスペクトルピークの半値幅と結晶化度Ic/Ia(結晶成分ピーク(520cm<sup>-1</sup>)/アモルファス成分ピーク(480cm<sup>-1</sup>)強度比)で表した。半値幅は9.5~9.7cm<sup>-1</sup>、結晶化度Ic/Ia比は12.4~13.8の範囲の値が得られており、膜質均一性についても良好な結果である。

#### 4.あとがき

次世代のフラットパネルディスプレイに大きな需要が期待されている低温ポリシリコン成膜技術と装置開発に取り組んだ。装置コンセプトは低温ポリシリコン成膜、ゲート絶縁膜成膜、予備加熱処理の一連の製造工程が可能なマルチチャンパー方式とした。その開発成果として、

(1)これまでの小型実験レベルから生産レベルの大型 基板対応の大型装置においても、従来の基本原理(ポリシ リコン成長メカニズム通りの膜特性が再現・確認できた。

(2) 基板サイズ600×720mm対応の製品開発において、

ホストコンピューターからの一括制御により自動基板搬送から成膜に必要なプロセスパラメーターの設定、運転 監視等の管理システムとしての開発成果が得られた。

本報告では割愛したが、TFT製作に必須のゲート絶縁膜の開発も同時に進めており、生産装置としての目標を達成できる成果も得られている<sup>(3)</sup>。

製品としては低温ポリシリコン成膜、ゲート絶縁膜成膜、予備加熱処理の一連の製造工程が可能なマルチチャンパー方式として製品開発を行っている。

製品としての性能では、不純物対策、高速成膜(高スループット)メンテナンス性、生産安定性などの課題をクリアし、2004年事業化を目指した開発を進めていきたい。また、低温ポリシリコン薄膜の応用としては、フラットパネルディスプレイのみならず、ポーラスシリコン、太陽電池、電子放出源等の次世代デバイスへの期待は大きく、今後の応用展開も視野に入れ開発を進めている。

本研究の一部は近畿経済産業局 新規産業創造技術開 発費補助金の制度を受けて実施している。

#### 参考文献

- (1) NEDO 超先端電子技術開発機構:平成11年度研究 成果報告書 次世代液晶プロセス基盤技術に関わる 先導研究開発報告書

- (2) 高橋、鞍谷、小野田、久保田、桐村:第63回応用物 理学会学術講演会 26p-G-2(2002.9)

- (3)高橋、鞍谷、小野田、久保田、桐村:第63回応用物 理学会学術講演会 24p-C-14(2002.9)

### 執筆者紹介

桐 村 浩 哉 技術開発研究所 プロセス研究センター ピーム・プラズマ応用第1グループ グループ長

久保田 清 技術開発研究所 プロセス研究センター ピーム・プラズマ応用第2グループ グループ長

小野田 正 敏 技術開発研究所 プロセス研究センター ビーム・プラズマ応用第2グループ 主任

鞍 谷 直 人 技術開発研究所 プロセス研究センター ピーム・プラズマ応用第1グループ

高 橋 英 治 技術開発研究所 プロセス研究センター ピーム・プラズマ応用第1グループ

小 寺 隆 志 技術開発研究所 プロセス研究センター ピーム・プラズマ応用第2グループ

渡 邊 哲 也 技術開発研究所 プロセス研究センター ビーム・プラズマ応用第2グループ

田 中 義 啓 技術開発研究所 プロセス研究センター ピーム・プラズマ応用第2グループ

米 田 均 技術開発研究所 プロセス研究センター ピーム・プラズマ応用第2グループ

岸 田 茂 明 技術開発研究所 プロセス研究センター ビーム・プラズマ応用第2グループ

緒 方 潔 技術開発研究所 プロセス研究センター 部長